Alexandru Nicolau – författare

Visar alla böcker från författaren Alexandru Nicolau. Handla med fri frakt och snabb leverans.

10 produkter

10 produkter

1 075 kr

Skickas inom 10-15 vardagar

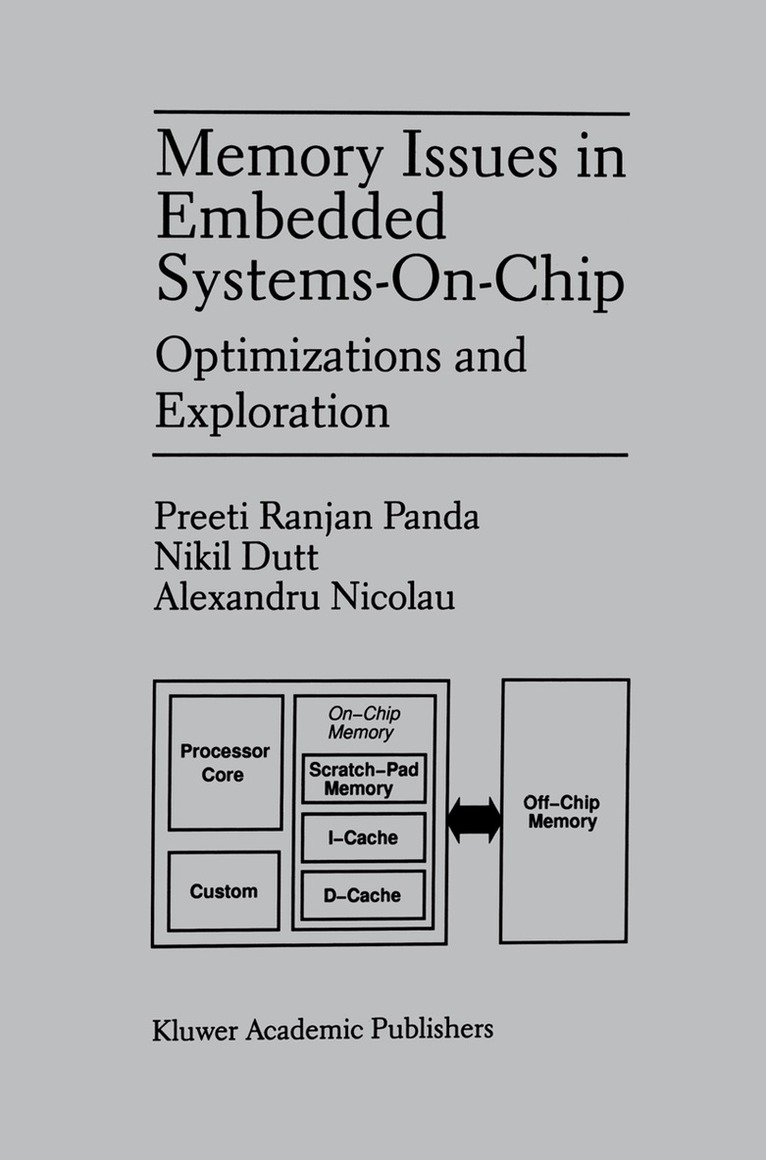

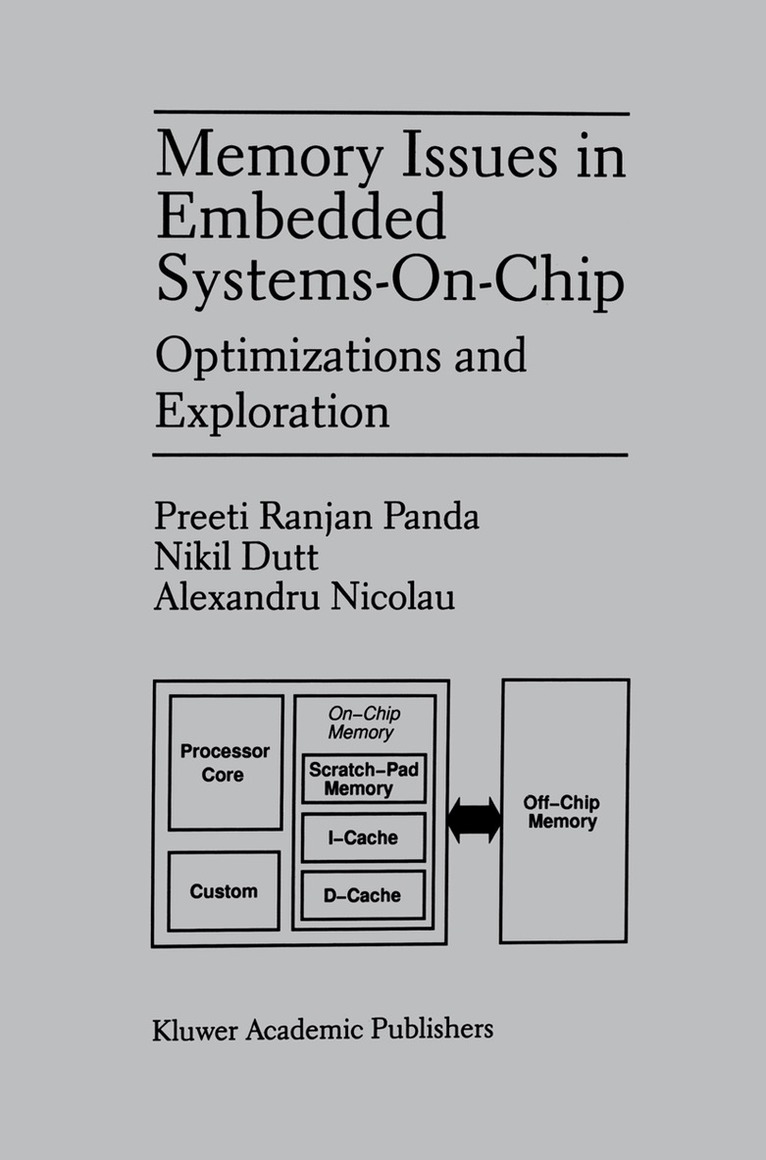

This text is designed for researchers and graduate students who wish to understand the research issues involved in memory system optimization and exploration for embedded systems-on-chip, and it is intended for designers of embedded systems who are migrating from a traditional micro-controllers centered, board-based design methodology to newer design methodologies using IP blocks for processor-core-based embedded systems-on-chip. Also, since the book illustrates a methodology for optimizing and exploring the memory configuration of embedded systems-on-chip, it is intended for managers and system designers who may be interested in the emerging capabilities of embedded systems-on-chip design methodologies for memory-intensive applications.

2 207 kr

Skickas inom 10-15 vardagar

This text offers the international community an opportunity to learn in-depth about key Japanese research efforts in the particular software domains of parallel programming and parallelizing compilers. These are important topics that strongly bear on the effectiveness and affordability of high performance computing systems. The chapters of this book convey a depiction of leading edge research efforts in Japan that focus on parallel software design, development, and optimization that could be obtained only through direct and personal interaction with the researchers themselves.

1 107 kr

Skickas inom 10-15 vardagar

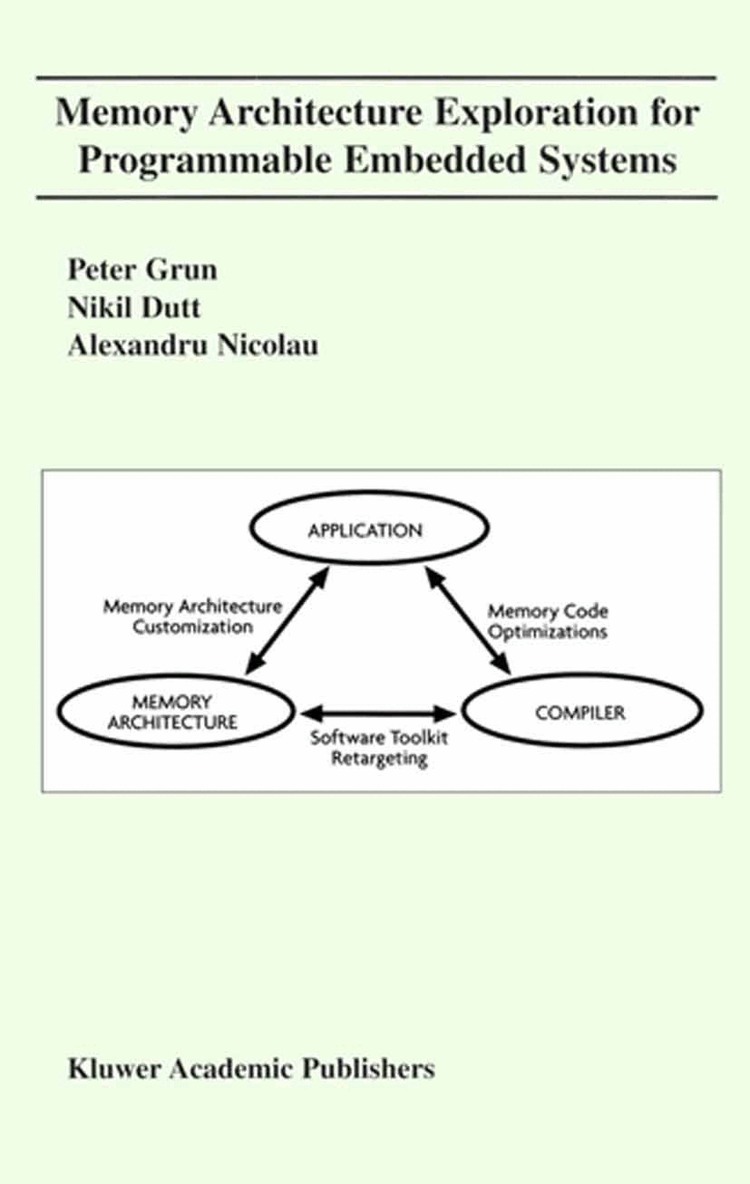

Memory Architecture Exploration for Programmable Embedded Systems addresses efficient exploration of alternative memory architectures, assisted by a "compiler-in-the-loop" that allows effective matching of the target application to the processor-memory architecture. This new approach for memory architecture exploration replaces the traditional black-box view of the memory system and allows for aggressive co-optimization of the programmable processor together with a customized memory system. The book concludes with a set of experiments demonstrating the utility of this exploration approach. The authors perform architecture and compiler exploration for a set of large, real-life benchmarks, uncovering promising memory configurations from different perspectives, such as cost, performance and power.

SPARK: A Parallelizing Approach to the High-Level Synthesis of Digital Circuits

Inbunden, Engelska, 2004

1 609 kr

Skickas inom 10-15 vardagar

Rapid advances in microelectronic integration and the advent of Systems-on-Chip have fueled the need for high-level synthesis, i.e., an automated approach to the synthesis of hardware from behavioral descriptions. SPARK: A Parallelizing High - Level Synthesis of Digital Circuits presents a novel approach to the high-level synthesis of digital circuits -- that of parallelizing high-level synthesis (PHLS). This approach uses aggressive code parallelizing and code motion techniques to discover circuit optimization opportunities beyond what is possible with traditional high-level synthesis. This PHLS approach addresses the problems of the poor quality of synthesis results and the lack of controllability over the transformations applied during the high-level synthesis of system descriptions with complex control flows, that is, with nested conditionals and loops. Also described are speculative code motion techniques and dynamic compiler transformations that optimize the circuit quality in terms of cycle time, circuit size and interconnect costs. We describe the SPARK parallelizing high-level synthesis framework in which we have implemented these techniques and demonstrate the utility of

1 075 kr

Skickas inom 10-15 vardagar

Memory Architecture Exploration for Programmable Embedded Systems addresses efficient exploration of alternative memory architectures, assisted by a "compiler-in-the-loop" that allows effective matching of the target application to the processor-memory architecture. This new approach for memory architecture exploration replaces the traditional black-box view of the memory system and allows for aggressive co-optimization of the programmable processor together with a customized memory system. The book concludes with a set of experiments demonstrating the utility of this exploration approach. The authors perform architecture and compiler exploration for a set of large, real-life benchmarks, uncovering promising memory configurations from different perspectives, such as cost, performance and power.

2 207 kr

Skickas inom 10-15 vardagar

Parallel Language and Compiler Research in Japan offers the international community an opportunity to learn in-depth about key Japanese research efforts in the particular software domains of parallel programming and parallelizing compilers. These are important topics that strongly bear on the effectiveness and affordability of high performance computing systems. The chapters of this book convey a comprehensive and current depiction of leading edge research efforts in Japan that focus on parallel software design, development, and optimization that could be obtained only through direct and personal interaction with the researchers themselves.

1 075 kr

Skickas inom 10-15 vardagar

Memory Issues in Embedded Systems-On-Chip: Optimizations and Explorations is designed for different groups in the embedded systems-on-chip arena. First, it is designed for researchers and graduate students who wish to understand the research issues involved in memory system optimization and exploration for embedded systems-on-chip. Second, it is intended for designers of embedded systems who are migrating from a traditional micro-controllers centered, board-based design methodology to newer design methodologies using IP blocks for processor-core-based embedded systems-on-chip. Also, since Memory Issues in Embedded Systems-on-Chip: Optimization and Explorations illustrates a methodology for optimizing and exploring the memory configuration of embedded systems-on-chip, it is intended for managers and system designers who may be interested in the emerging capabilities of embedded systems-on-chip design methodologies for memory-intensive applications.

SPARK: A Parallelizing Approach to the High-Level Synthesis of Digital Circuits

Häftad, Engelska, 2013

1 609 kr

Skickas inom 10-15 vardagar

Rapid advances in microelectronic integration and the advent of Systems-on-Chip have fueled the need for high-level synthesis, i.e., an automated approach to the synthesis of hardware from behavioral descriptions. SPARK: A Parallelizing Approach to the High - Level Synthesis of Digital Circuits presents a novel approach to the high-level synthesis of digital circuits -- that of parallelizing high-level synthesis (PHLS). This approach uses aggressive code parallelizing and code motion techniques to discover circuit optimization opportunities beyond what is possible with traditional high-level synthesis. This PHLS approach addresses the problems of the poor quality of synthesis results and the lack of controllability over the transformations applied during the high-level synthesis of system descriptions with complex control flows, that is, with nested conditionals and loops. Also described are speculative code motion techniques and dynamic compiler transformations that optimize the circuit quality in terms of cycle time, circuit size and interconnect costs. We describe the SPARK parallelizing high-level synthesis framework in which we have implemented these techniques and demonstrate the utility of SPARK's PHLS approach using designs derived from multimedia and image processing applications. We also present a case study of an instruction length decoder derived from the Intel Pentium-class of microprocessors. This case study serves as an example of a typical microprocessor functional block with complex control flow and demonstrates how our techniques are useful for such designs. SPARK: A Parallelizing Approach to the High - Level Synthesis of Digital Circuits is targeted mainly to embedded system designers and researchers. This includes people working on design and design automation. The book is useful for researchers and design automation engineers who wish to understand how the main problems hindering the adoption of high-level synthesis among designers.

915 kr

Skickas inom 10-15 vardagar

This book precisely formulates and simplifies the presentation of Instruction Level Parallelism (ILP) compilation techniques. It uniquely offers consistent and uniform descriptions of the code transformations involved. Due to the ubiquitous nature of ILP in virtually every processor built today, from general purpose CPUs to application-specific and embedded processors, this book is useful to the student, the practitioner and also the researcher of advanced compilation techniques. With an emphasis on fine-grain instruction level parallelism, this book will also prove interesting to researchers and students of parallelism at large, in as much as the techniques described yield insights that go beyond superscalar and VLIW (Very Long Instruction Word) machines compilation and are more widely applicable to optimizing compilers in general. ILP techniques have found wide and crucial application in Design Automation, where they have been used extensively in the optimization of performanceas well as area and power minimization of computer designs.

648 kr

Skickas inom 10-15 vardagar

This book precisely formulates and simplifies the presentation of Instruction Level Parallelism (ILP) compilation techniques.