Görschwin Fey – författare

Visar alla böcker från författaren Görschwin Fey. Handla med fri frakt och snabb leverans.

9 produkter

9 produkter

1 598 kr

Skickas inom 10-15 vardagar

VLSI CADhas greatly bene?ted from the use of reduced ordered Binary Decision Diagrams (BDDs) and the clausal representation as a problem of Boolean Satis?ability (SAT), e.g. in logic synthesis, ver- cation or design-for-testability. In recent practical applications, BDDs are optimized with respect to new objective functions for design space exploration. The latest trends show a growing number of proposals to fuse the concepts of BDD and SAT. This book gives a modern presentation of the established as well as of recent concepts. Latest results in BDD optimization are given, c- ering di?erent aspects of paths in BDDs and the use of e?cient lower bounds during optimization. The presented algorithms include Branch ? and Bound and the generic A -algorithm as e?cient techniques to - plore large search spaces. ? The A -algorithm originates from Arti?cial Intelligence (AI), and the EDA community has been unaware of this concept for a long time. Re- ? cently, the A -algorithm has been introduced as a new paradigm to explore design spaces in VLSI CAD. Besides AI search techniques, the book also discusses the relation to another ?eld of activity bordered to VLSI CAD and BDD optimization: the clausal representation as a SAT problem.

1 068 kr

Skickas inom 10-15 vardagar

The size of technically producible integrated circuits increases continuously. But the ability to design and verify these circuits does not keep up with this development. Therefore, today’s design ?ow has to be improved to achieve a higher productivity. In this book the current design methodology and ver- cation methodology are analyzed, a number of de?ciencies are identi?ed, and solutions are suggested. Improvements in the methodology as well as in the underlying algorithms are proposed. An in-depth presentation of preliminary concepts makes the book self-contained. Based on this foundation major - sign problems are targeted. In particular, a complete tool ?ow for Synthesis for Testability of SystemC descriptions is presented. The resulting circuits are completely testable and test pattern generation in polynomial time is possible. Veri?cation issues are covered in even more detail. A whole new paradigm for formal design veri?cation is suggested. This is based upon design und- standing, the automatic generation of properties, and powerful tool support for debugging failures. All these new techniques are empirically evaluated and - perimental results are provided. As a result, an enhanced design ?ow is created that provides more automation (i.e. better usability) and reduces the probability of introducing conceptual errors (i.e. higher robustness). Acknowledgments We would like to thank all members of the research group for computer arc- tecture in Bremen for the helpful discussions and the great atmosphere during work and research.

1 598 kr

Skickas inom 10-15 vardagar

The size of technically producible integrated circuits increases continuously. But the ability to design and verify these circuits does not keep up with this development. Therefore today's design flow has to be improved to achieve a higher productivity. In Robustness and Usability in Modern Design Flows the current design methodology and verification methodology are analyzed, a number of deficiencies are identified and solutions suggested. Improvements in the methodology as well as in the underlying algorithms are proposed. An in-depth presentation of preliminary concepts makes the book self-contained. Based on this foundation major design problems are targeted. In particular, a complete tool flow for Synthesis for Testability of SystemC descriptions is presented. The resulting circuits are completely testable and test pattern generation in polynomial time is possible. Verification issues are covered in even more detail. A whole new paradigm for formal design verification is suggested. This is based upon design understanding, the automatic generation of properties and powerful tool support for debugging failures.All these new techniques are empirically evaluated and experimental results are provided. As a result, an enhanced design flow is created that provides more automation (i.e. better usability) and reduces the probability of introducing conceptual errors (i.e. higher robustness).

538 kr

Skickas inom 10-15 vardagar

This book describes automated debugging approaches for the bugs and the faults which appear in different abstraction levels of a hardware system. The authors employ a transaction-based debug approach to systems at the transaction-level, asserting the correct relation of transactions. The automated debug approach for design bugs finds the potential fault candidates at RTL and gate-level of a circuit. Debug techniques for logic bugs and synchronization bugs are demonstrated, enabling readers to localize the most difficult bugs. Debug automation for electrical faults (delay faults)finds the potentially failing speedpaths in a circuit at gate-level. The various debug approaches described achieve high diagnosis accuracy and reduce the debugging time, shortening the IC development cycle and increasing the productivity of designers.Describes a unified framework for debug automation used at both pre-silicon and post-silicon stages;Provides approaches for debug automation of a hardware system at different levels of abstraction, i.e., chip, gate-level, RTL and transaction level;Includes techniques for debug automation of design bugs and electrical faults, as well as an infrastructure to debug NoC-based multiprocessor SoCs.

538 kr

Skickas inom 10-15 vardagar

This book describes automated debugging approaches for the bugs and the faults which appear in different abstraction levels of a hardware system. The authors employ a transaction-based debug approach to systems at the transaction-level, asserting the correct relation of transactions. The automated debug approach for design bugs finds the potential fault candidates at RTL and gate-level of a circuit. Debug techniques for logic bugs and synchronization bugs are demonstrated, enabling readers to localize the most difficult bugs. Debug automation for electrical faults (delay faults)finds the potentially failing speedpaths in a circuit at gate-level. The various debug approaches described achieve high diagnosis accuracy and reduce the debugging time, shortening the IC development cycle and increasing the productivity of designers.Describes a unified framework for debug automation used at both pre-silicon and post-silicon stages;Provides approaches for debug automation of a hardware system at different levels of abstraction, i.e., chip, gate-level, RTL and transaction level;Includes techniques for debug automation of design bugs and electrical faults, as well as an infrastructure to debug NoC-based multiprocessor SoCs.

1 141 kr

Skickas inom 5-8 vardagar

Eingebettete Systeme übernehmen zentrale Steueraufgaben im täglichen Leben. In der Energieversorgung oder im Transportwesen würde ein Ausfall der Systeme fatale Auswirkungen haben. Der Nutzer verlässt sich aber auf ein fehlerfreies Funktionieren des Systems. Die Funktionstüchtigkeit der Schaltkreise zu garantieren, ist das Ziel des Testens – und das mit geringen Kosten, da jeder Chip nach der Produktion separat getestet werden muss.

1 069 kr

Skickas inom 10-15 vardagar

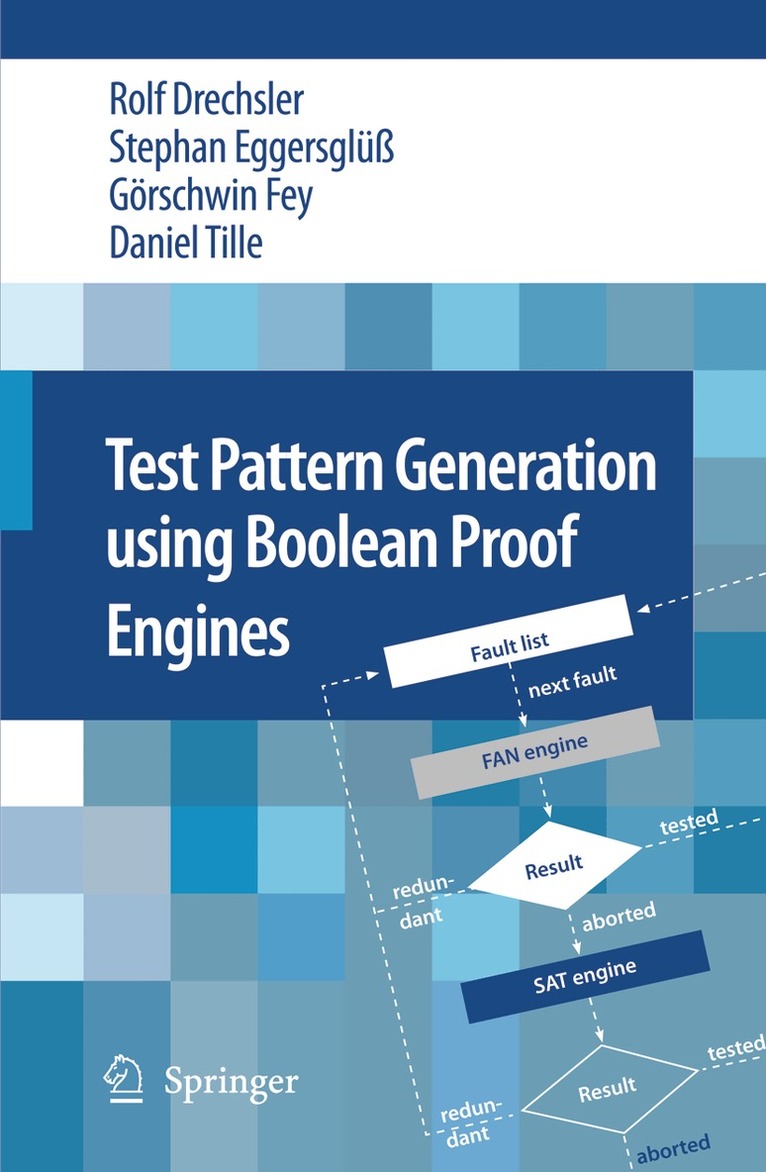

In Test Pattern Generation using Boolean Proof Engines, we give an introduction to ATPG. The basic concept and classical ATPG algorithms are reviewed. Then, the formulation as a SAT problem is considered. As the underlying engine, modern SAT solvers and their use on circuit related problems are comprehensively discussed. Advanced techniques for SAT-based ATPG are introduced and evaluated in the context of an industrial environment. The chapters of the book cover efficient instance generation, encoding of multiple-valued logic, usage of various fault models, and detailed experiments on multi-million gate designs. The book describes the state of the art in the field, highlights research aspects, and shows directions for future work.

1 069 kr

Skickas inom 10-15 vardagar

The size of technically producible integrated circuits increases continuously. But the ability to design and verify these circuits does not keep up with this development. Therefore, today’s design ?ow has to be improved to achieve a higher productivity. In this book the current design methodology and ver- cation methodology are analyzed, a number of de?ciencies are identi?ed, and solutions are suggested. Improvements in the methodology as well as in the underlying algorithms are proposed. An in-depth presentation of preliminary concepts makes the book self-contained. Based on this foundation major - sign problems are targeted. In particular, a complete tool ?ow for Synthesis for Testability of SystemC descriptions is presented. The resulting circuits are completely testable and test pattern generation in polynomial time is possible. Veri?cation issues are covered in even more detail. A whole new paradigm for formal design veri?cation is suggested. This is based upon design und- standing, the automatic generation of properties, and powerful tool support for debugging failures. All these new techniques are empirically evaluated and - perimental results are provided. As a result, an enhanced design ?ow is created that provides more automation (i.e. better usability) and reduces the probability of introducing conceptual errors (i.e. higher robustness). Acknowledgments We would like to thank all members of the research group for computer arc- tecture in Bremen for the helpful discussions and the great atmosphere during work and research.

1 069 kr

Skickas inom 10-15 vardagar

In Test Pattern Generation using Boolean Proof Engines, we give an introduction to ATPG. The basic concept and classical ATPG algorithms are reviewed. Then, the formulation as a SAT problem is considered. As the underlying engine, modern SAT solvers and their use on circuit related problems are comprehensively discussed. Advanced techniques for SAT-based ATPG are introduced and evaluated in the context of an industrial environment. The chapters of the book cover efficient instance generation, encoding of multiple-valued logic, usage of various fault models, and detailed experiments on multi-million gate designs. The book describes the state of the art in the field, highlights research aspects, and shows directions for future work.