Janick Bergeron – författare

Visar alla böcker från författaren Janick Bergeron. Handla med fri frakt och snabb leverans.

7 produkter

7 produkter

1 654 kr

Skickas inom 10-15 vardagar

Functional verification remains one of the single biggest challenges in the development of complex system-on-chip (SoC) devices. Despite the introduction of successive new technologies, the gap between design capability and verification confidence continues to widen. The biggest problem is that these diverse new technologies have led to a proliferation of verification point tools, most with their own languages and methodologies. Fortunately, a solution is at hand. SystemVerilog is a unified language that serves both design and verification engineers by including RTL design constructs, assertions and a rich set of verification constructs. SystemVerilog is an industry standard that is well supported by a wide range of verification tools and platforms. A single language fosters the development of a unified simulation-based verification tool or platform.Consolidation of point tools into a unified platform and convergence to a unified language enable the development of a unified verification methodology that can be used on a wide range of SoC projects. ARM and Synopsys have worked together to define just such a methodology in the Verification Methodology Manual for SystemVerilog. This book is based upon best verification practices by ARM, Synopsys and their customers.Verification Methodology Manual for SystemVerilog is a blueprint for verification success, guiding SoC teams in building a reusable verification environment taking full advantage of design-for-verification techniques, constrained-random stimulus generation, coverage-driven verification, formal verification and other advanced technologies to help solve their current and future verification problems.This book is appropriate for anyone involved in the design or verification of a complex chip or anyone who would like to know more about the capabilities of SystemVerilog. Following the Verification Methodology Manual for SystemVerilog will give SoC development teams and project managers the confidence needed to tape out a complex design, secure in the knowledge that the chip will function correctly in the real world.

2 203 kr

Skickas inom 10-15 vardagar

If you survey hardware design groups, you will learn that between 60% and 80% of their effort is dedicated to verification. This may seem unusually large, but I include in "verification" all debugging and correctness checking activities, not just writing and running testbenches. Every time a hardware designer pulls up a waveform viewer, he or she performs a verification task. With today’s ASIC and FPGA sizes and geometries, getting a design to fit and run at speed is no longer the main challenge. It is to get the right design, working as intended, at the right time. Unlike synthesizable coding, there is no particular coding style nor language required for verification. The freedom of using any l- guage that can be interfaced to a simulator and of using any features of that language has produced a wide array of techniques and approaches to verification. The continued absence of constraints and historical shortage of available expertise in verification, c- pled with an apparent under-appreciation of and under-investment in the verification function, has resulted in several different ad hoc approaches. The consequences of an informal, ill-equipped and understaffed verification process can range from a non-functional design requiring several re-spins, through a design with only a s- set of the intended functionality, to a delayed product shipment.

2 418 kr

Skickas inom 10-15 vardagar

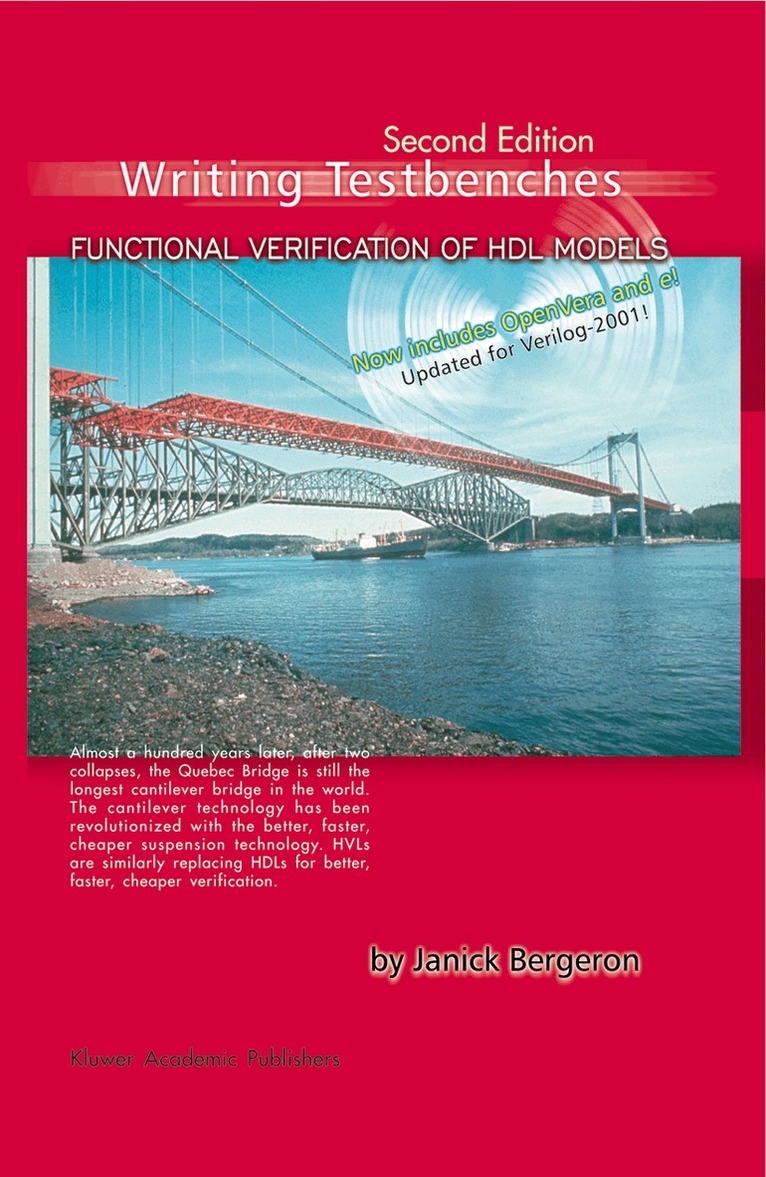

This second edition presents the most up-to-date verification techniques to produce fully functional first silicon ASICs, systems-on-a-chip (SoC), boards and entire systems. Topics included are: discussions on openvera and e; approaches for writing constrainable random stimulus generators; strategies for making testbenches self-checking; a clear blueprint of a verification process that aims for first time success; recent advances in functional verification such as coverage-driven verification process; VHDL and Verilog language semantics; the semantics are presented in new verification-oriented languages; techniques for applying stimulus and monitoring the response of a design; behavioural modelling using non-synthesizeable constructs and coding style; and updated for Verilog 2001.

1 391 kr

Skickas inom 10-15 vardagar

If you survey hardware design groups, you will learn that between 60% and 80% of their effort is dedicated to verification. This may seem unusually large, but I include in "verification" all debugging and correctness checking activities, not just writing and running testbenches. Every time a hardware designer pulls up a waveform viewer, he or she performs a verification task. With today’s ASIC and FPGA sizes and geometries, getting a design to fit and run at speed is no longer the main challenge. It is to get the right design, working as intended, at the right time. Unlike synthesizable coding, there is no particular coding style nor language required for verification. The freedom of using any l- guage that can be interfaced to a simulator and of using any features of that language has produced a wide array of techniques and approaches to verification. The continued absence of constraints and historical shortage of available expertise in verification, c- pled with an apparent under-appreciation of and under-investment in the verification function, has resulted in several different ad hoc approaches. The consequences of an informal, ill-equipped and understaffed verification process can range from a non-functional design requiring several re-spins, through a design with only a s- set of the intended functionality, to a delayed product shipment.

2 348 kr

Skickas inom 10-15 vardagar

mental improvements during the same period. What is clearly needed in verification techniques and technology is the equivalent of a synthesis productivity breakthrough. In the second edition of Writing Testbenches, Bergeron raises the verification level of abstraction by introducing coverage-driven constrained-random transaction-level self-checking testbenches all made possible through the introduction of hardware verification languages (HVLs), such as e from Verisity and OpenVera from Synopsys. The state-of-art methodologies described in Writing Test benches will contribute greatly to the much-needed equivalent of a synthesis breakthrough in verification productivity. I not only highly recommend this book, but also I think it should be required reading by anyone involved in design and verification of today's ASIC, SoCs and systems. Harry Foster Chief Architect Verplex Systems, Inc. xviii Writing Testbenches: Functional Verification of HDL Models PREFACE If you survey hardware design groups, you will learn that between 60% and 80% of their effort is now dedicated to verification.

1 178 kr

Skickas inom 10-15 vardagar

Functional verification remains one of the single biggest challenges in the development of complex system-on-chip (SoC) devices. Despite the introduction of successive new technologies, the gap between design capability and verification confidence continues to widen. The biggest problem is that these diverse new technologies have led to a proliferation of verification point tools, most with their own languages and methodologies. Fortunately, a solution is at hand. SystemVerilog is a unified language that serves both design and verification engineers by including RTL design constructs, assertions and a rich set of verification constructs. SystemVerilog is an industry standard that is well supported by a wide range of verification tools and platforms. A single language fosters the development of a unified simulation-based verification tool or platform.Consolidation of point tools into a unified platform and convergence to a unified language enable the development of a unified verification methodology that can be used on a wide range of SoC projects. ARM and Synopsys have worked together to define just such a methodology in the Verification Methodology Manual for SystemVerilog. This book is based upon best verification practices by ARM, Synopsys and their customers.Verification Methodology Manual for SystemVerilog is a blueprint for verification success, guiding SoC teams in building a reusable verification environment taking full advantage of design-for-verification techniques, constrained-random stimulus generation, coverage-driven verification, formal verification and other advanced technologies to help solve their current and future verification problems.This book is appropriate for anyone involved in the design or verification of a complex chip or anyone who would like to know more about the capabilities of SystemVerilog. Following the Verification Methodology Manual for SystemVerilog will give SoC development teams and project managers the confidence needed to tape out a complex design, secure in the knowledge that the chip will function correctly in the real world.

1 178 kr

Skickas inom 10-15 vardagar

CHAPTER 6 Architecting Testbenches 221 Reusable Verification Components 221 Procedural Interface 225 Development Process 226 Verilog Implementation 227 Packaging Bus-Functional Models 228 Utility Packages 231 VHDL Implementation 237 Packaging Bus-Functional Procedures 238 240 Creating a Test Harness 243 Abstracting the Client/Server Protocol Managing Control Signals 246 Multiple Server Instances 247 Utility Packages 249 Autonomous Generation and Monitoring 250 Autonomous Stimulus 250 Random Stimulus 253 Injecting Errors 255 Autonomous Monitoring 255 258 Autonomous Error Detection Input and Output Paths 258 Programmable Testbenches 259 Configuration Files 260 Concurrent Simulations 261 Compile-Time Configuration 262 Verifying Configurable Designs 263 Configurable Testbenches 265 Top Level Generics and Parameters 266 Summary 268 CHAPTER 7 Simulation Management 269 Behavioral Models 269 Behavioral versus Synthesizable Models 270 Example of Behavioral Modeling 271 Characteristics of a Behavioral Model 273 x Writing Testbenches: Functional Verification of HDL Models Modeling Reset 276 Writing Good Behavioral Models 281 Behavioral Models Are Faster 285 The Cost of Behavioral Models 286 The Benefits of Behavioral Models 286 Demonstrating Equivalence 289 Pass or Fail? 289 Managing Simulations 292 294 Configuration Management Verilog Configuration Management 295 VHDL Configuration Management 301 SDF Back-Annotation 305 Output File Management 309 Regression 312 Running Regressions 313 Regression Management 314 Summary 316 APPENDIX A Coding Guidelines 317 Directory Structure 318 VHDL Specific 320 Verilog Specific 320 General Coding Guidelines 321 Comments 321 Layout 323 Syntax 326 Debugging 329 Naming Guidelines 329 Capitalization 330 Identifiers 332 Constants 334 334 HDL SpecificFilenames 336 HDL Coding Guidelines 336 337 Structure 337 Layout